## **Preliminary Information**

## 32-Channel High Voltage Sample and Hold Amplifier Array

#### **Features**

- ☐ 32 independent high voltage amplifiers

- 300V operating voltage

- 295V output voltage

- ☐ 2.2V/µs typical output slew rate

- ☐ Adjustable output current source limit

- Adjustable output current sink limit

- Internal closed loop gain of 72V/V

- ☐ 12M feedback impedance

- □ Layout ideal for die applications

#### **Application**

- ☐ MEMS (microelctromechanical systems) driver

- Piezoelectric transducer driver

- ☐ Optical crosspoint switches (using MEMS technology)

## **Block Diagram**

# APPRING C DVdd o DV-60 62.0

#### **General Description**

The Supertex HV257 is a 32-channel high voltage sample and hold amplifier array integrated circuit. It operates on a single high voltage supply, up to 300V, and two low voltage supplies, V<sub>DD</sub> and V<sub>NN</sub>.

All 32 sample and hold circuits share a common analog input, Vsig. The individual sample and hold circuits are selected by a 5 to 32 logic decoder. The sampled voltage on the holding capacitor is buffered by a low voltage amplifier and amplified by a high voltage amplifier with a closed loop gain of 72V/V. The internal closed loop gain is set for an input voltage range of 0V to 4.096V. The input voltage can be up to 5.0V, but the output will saturate. The maximum output voltage swing is 5V below the  $V_{\mbox{\footnotesize PP}}$ high voltage supply. The outputs can drive capacitive loads of up to 3000pF.

The maximum output source and sink current can be adjusted by using two external resistors. An external R<sub>SOURCE</sub> resistor controls the maximum sourcing current and an external R<sub>SINK</sub> resistor controls the maximum sinking current. The current limit is approximately 12.5V divided by the external resistor value. The setting is common for all 32 outputs. A low voltage silicon junction diode is made available to help monitor the die temperature.

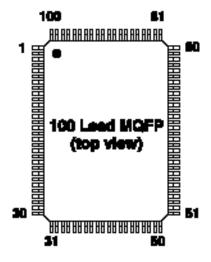

# **Ordering Information**

| Device | Maximum Output | Nominal Closed | Package       | Options |

|--------|----------------|----------------|---------------|---------|

| Device | Voltage        | Loop Gain      | 100 Lead MQFP | Die     |

| HV257  | 295V           | 72V/V          | HV257FG       | HV257X  |

# **Absolute Maximum Ratings\***

| V <sub>PP</sub> , High voltage supply                  | 310V                      |

|--------------------------------------------------------|---------------------------|

| AV <sub>DD</sub> , Analog low voltage positive supply  | 8.0V                      |

| DV <sub>DD</sub> , Digital low voltage positive supply | 8.0V                      |

| AV <sub>NN</sub> , Analog low voltage negative supply  | -7.0V                     |

| DV <sub>NN</sub> , Digital low voltage negative supply | -7.0V                     |

| Logic input voltage                                    | -0.5V to DV <sub>DD</sub> |

| V <sub>IN</sub> , Analog input signal                  | 0V to 6.0V                |

| Storage temperature range                              | -65 C to 150°C            |

| Maximum junction temperature                           | 150°C                     |

|                                                        |                           |

<sup>\*</sup>Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

$\mathsf{HV}_\mathsf{OUT}$  sourcing current limiting range

${\rm HV}_{\rm OUT}$  sinking current limiting range

DC channel to channel crosstalk

External resistance range for setting current

External resistance range for setting current

Power supply rejection ratio for  $\rm V_{PP}, \, \rm V_{DD}, \, and \, \rm V_{NN}$

ISOURCE

$\mathsf{R}_{\mathsf{SOURCE}}$

$R_{SINK}$

CT<sub>DC</sub> PSRR source limit

$\mathsf{I}_{\underline{\mathsf{SINK}}}$

#### Electrical Characteristics (Over operating conditions unless otherwise noted.)

| Symbol            | Parameter                                            | Min  | Тур  | Max                | Units | Conditions                                                |

|-------------------|------------------------------------------------------|------|------|--------------------|-------|-----------------------------------------------------------|

| Operatir          | ng Conditons                                         |      |      |                    |       |                                                           |

| V <sub>PP</sub>   | High voltage positive supply                         | 125  |      | 300                | V     |                                                           |

| V <sub>DD</sub>   | Low voltage positive supply                          | 6.0  |      | 7.5                | V     |                                                           |

| V <sub>NN</sub>   | Low voltage negative supply                          | -4.5 |      | -6.5               | V     |                                                           |

| I <sub>PP</sub>   | V <sub>PP</sub> supply current                       |      |      | 0.8                | mA    | V <sub>PP</sub> =300V, All HV <sub>OUT</sub> =0V, No Load |

| I <sub>DD</sub>   | V <sub>DD</sub> supply current                       |      |      | 4.3                | mA    | V <sub>DD</sub> = 6.0V to 7.5V                            |

| I <sub>NN</sub>   | V <sub>NN</sub> supply current                       | -5.2 |      |                    | mA    | V <sub>NN</sub> = -4.5V to -6.5V                          |

| T <sub>J</sub>    | Junction temperature range                           | -10  |      | 125                | °C    |                                                           |

| High Vo           | oltage Amplifier                                     |      |      |                    |       |                                                           |

| HV <sub>OUT</sub> | HV <sub>OUT</sub> voltage swing                      | 0    |      | V <sub>PP</sub> -5 | V     |                                                           |

| V <sub>INOS</sub> | Input voltage range                                  |      |      | ±50                | mV    | Input referred.                                           |

| SR                | HV <sub>OUT</sub> slew rate rise                     |      | 2.2  |                    | V/µs  | No Load                                                   |

| SK                | HV <sub>OUT</sub> slew rate fall                     |      | 2.0  |                    | V/µs  | No Load                                                   |

| BW                | HV <sub>OUT</sub> -3dB channel bandwidth             |      | 4.0  |                    | KHz   | V <sub>PP</sub> =300V                                     |

| A <sub>O</sub>    | Open loop gain                                       | 70   | 100  |                    | dB    |                                                           |

| A <sub>V</sub>    | Closed loop gain                                     | 68.4 | 72.0 | 75.6               | V/V   |                                                           |

| R <sub>FB</sub>   | Feedback resistance from HV <sub>OUT</sub> to ground | 9.6  | 12   |                    | М     |                                                           |

| C <sub>LOAD</sub> | HV <sub>OUT</sub> capacitive load                    | 0    |      | 3000               | pF    |                                                           |

|                   |                                                      |      |      |                    |       |                                                           |

550

550

385

385

25

25

-80

-40

715

715

250

250

μΑ

μΑ

Κ

Κ

dΒ

dΒ

$R_{SOURCE} = 25K$

$R_{SINK} = 25K$

## Sample and Hold

| Symbol         | Parameter                                     | Min | Тур | Max | Units | Conditions |

|----------------|-----------------------------------------------|-----|-----|-----|-------|------------|

| Vped           | Pedestal Voltage                              |     |     | TBD | mV    |            |

| Rsw            | Sample and Hold Switch resistance             |     | 5.0 | TBD | K     |            |

| C <sub>H</sub> | Samp and Hold capacitor                       |     | 10  | TBD | pF    |            |

| Rdroop         | Droop rate during hold time relative to input |     |     | TBD | V/s   |            |

| Vsig           | Input voltage range                           | 0   |     | 5.0 | V     |            |

#### **Logic Decoder**

| Symbol | Parameter                       | Min  | Тур | Max             | Units | Conditions            |

|--------|---------------------------------|------|-----|-----------------|-------|-----------------------|

| tsu    | Set-up time-address to enable   | 75   |     |                 | ns    |                       |

| th     | Hold time-address to enable bar | 75   |     |                 | ns    |                       |

| Vih    | Input logic high voltage        | 2.4  |     | V <sub>DD</sub> | V     |                       |

| Vil    | Input logic low voltage         | 0    |     | 1.2             | V     |                       |

| lih    | Input logic high current        |      |     | 1.0             | μA    | Vih = V <sub>DD</sub> |

| lil    | Input logic low current         | -1.0 |     |                 | μΑ    | Vil = 0V              |

#### **Diode**

| Symbol         | Parameter                              | Min | Тур | Max | Units | Conditions                 |

|----------------|----------------------------------------|-----|-----|-----|-------|----------------------------|

| PIV            | Peak inverse voltage                   |     |     | 5.0 | V     | cathode to anode           |

| V <sub>F</sub> | Forward diode drop                     |     |     | 0.8 | V     | If=2.0mA, anode to cathode |

| I <sub>F</sub> | Forward diode current                  |     |     | 2.0 | mA    | anode to cathode           |

| T <sub>C</sub> | V <sub>F</sub> temperature coefficient |     | TBD |     | mV/°C | anode to cathode           |

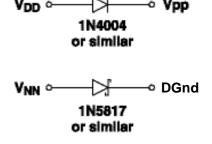

## **Power Up/Down Sequence**

The device can be damaged due to improper power up / down sequence. To prevent damage, please follow the acceptable power up /down sequences and add two external diodes as shown in the diagram below. The first diode is a high voltage diode across  $V_{PP}$  and  $V_{DD}$  where the anode of the diode is connected to  $V_{DD}$  and the cathode of the diode is connected to Vpp. Any low current high voltage diode such as a 1N4004 will be adequate. The second diode is a schottky diode across  $V_{NN}$  and DGnd where the anode of the schottky diode is connected to  $V_{NN}$  and the cathode is connected to DGnd. Any low current schottky diode such as a 1N5817 will be adequate.

#### **Acceptable Power Up Sequences**

1)  $V_{PP}$  2)  $V_{NN}$  3)  $V_{DD}$  4) Inputs & Anode 1)  $V_{DD}$  2)  $V_{NN}$  3)  $V_{PP}$  4) Inputs & Anode

#### **Acceptable Power Down Sequences**

1) Inputs & Anode 2)  $V_{PP}$  3)  $V_{DD}$  4)  $V_{NN}$  1) Inputs & Anode 2)  $V_{DD}$  3)  $V_{NN}$  4)  $V_{PP}$

# **Truth Table**

| A4 | А3 | A2 | <b>A</b> 1 | A0 | EN | Selected S/H |

|----|----|----|------------|----|----|--------------|

| L  | L  | L  | L          | L  | Н  | 0            |

| L  | L  | L  | L          | Н  | Н  | 1            |

| L  | L  | L  | Н          | L  | Н  | 2            |

| L  | L  | L  | Н          | Н  | Н  | 3            |

| •  |    |    | :          |    |    | •            |

| •  |    |    | •          |    |    | •            |

| Н  | Н  | Н  | L          | Н  | Н  | 29           |

| Н  | Н  | Н  | Н          | L  | Н  | 30           |

Н

Χ

Н

31

All Open

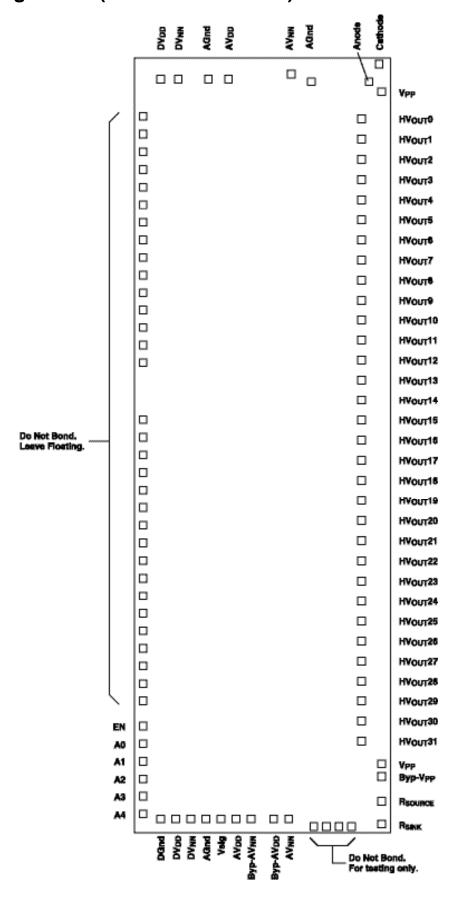

# **Pin Description**

Χ

Н

Χ

Н

Χ

| V <sub>PP</sub>                             | High voltage positive supply. There are two pads.                                                                                                                         |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B <sub>YP</sub> -V <sub>PP</sub>            | A low voltage 1.0 to 10nF decoupling capacitor across $\rm V_{PP}$ and $\rm B_{YP}\text{-}V_{PP}$ is required.                                                            |

| AV <sub>DD</sub>                            | Analog low voltage positive supply. This should be at the same potential as $DV_DD.$ There are two pads.                                                                  |

| $B_YP	ext{-}AV_DD$                          | A low voltage 1.0 to 10nF decoupling capacitor across ${\rm AV}_{\rm DD}$ and ${\rm B}_{\rm YP}{\rm -AV}_{\rm DD}$ is required.                                           |

| AV <sub>NN</sub>                            | Analog low voltage negative supply. This should be the same potential as $DV_NN$ . There are two pads.                                                                    |

| B <sub>YP</sub> -AV <sub>NN</sub>           | A low voltage 1.0 to 10nF decoupling capacitor across ${\rm AV}_{\rm NN}$ and ${\rm B}_{\rm YP}{\rm -AV}_{\rm NN}$ is required.                                           |

| DV <sub>DD</sub>                            | Digital low voltage positive supply. This should be the same potential as $AV_DD.$ There are two pads.                                                                    |

| DV <sub>NN</sub>                            | Digital low voltage negative supply. This should be the same potential as ${\rm AV}_{\rm NN}.$ There are two pads.                                                        |

| DGND                                        | Digital ground.                                                                                                                                                           |

| AGND                                        | Analog ground. There are three pads. They need to be externally connected together.                                                                                       |

| A0 to A4                                    | Decoder logic inputs. Addressed channel will close the sample and hold switch. Sample and hold switches for unaddressed channels are kept open.                           |

| EN                                          | Active logic high input. Logic low will keep sample and hold switches open.                                                                                               |

| Vsig                                        | Common input signal for all 32 sample and hold circuits.                                                                                                                  |

| R <sub>SOURCE</sub>                         | External resistor from R <sub>SOURCE</sub> to V <sub>NN</sub> sets output current sourcing limit. Current limit is approximately 12.5V divided by Rsource resistor value. |

| R <sub>SINK</sub>                           | External resistor from $R_{SINK}$ to $V_{NN}$ sets output current sinking limit. Current limit is approximately 12.5V divided by $R_{SINK}$ resistor value.               |

| Anode                                       | Anode side of a low voltage silicon diode that can be used to monitor die temperature.                                                                                    |

| Cathode                                     | Cathode side of a low voltage silicon diode that can be used to monitor die temperature.                                                                                  |

| HV <sub>OUT</sub> 0 to HV <sub>OUT</sub> 31 | Amplifier outputs.                                                                                                                                                        |

| Pin # | Function             |

|-------|----------------------|

| 1     | HV <sub>OUT</sub> 31 |

| 2     | HV <sub>OUT</sub> 30 |

| 3     | HV <sub>OUT</sub> 29 |

| 4     | HV <sub>OUT</sub> 28 |

| 5     | HV <sub>OUT</sub> 27 |

| 6     | HV <sub>OUT</sub> 26 |

| 7     | HV <sub>OUT</sub> 25 |

| 8     | HV <sub>OUT</sub> 24 |

| 9     | HV <sub>OUT</sub> 23 |

| 10    | HV <sub>OUT</sub> 22 |

| 11    | HV <sub>OUT</sub> 21 |

| 12    | HV <sub>OUT</sub> 20 |

| 13    | HV <sub>out</sub> 19 |

| 14    | HV <sub>out</sub> 18 |

| 15    | HV <sub>out</sub> 17 |

| 16    | HV <sub>out</sub> 16 |

| 17    | HV <sub>out</sub> 15 |

| 18    | HV <sub>OUT</sub> 14 |

| 19    | HV <sub>out</sub> 13 |

| 20    | HV <sub>out</sub> 12 |

| 21    | HV <sub>OUT</sub> 11 |

| 22    | HV <sub>out</sub> 10 |

| 23    | HV <sub>out</sub> 9  |

| 24    | HV <sub>OUT</sub> 8  |

| 25    | HV <sub>OUT</sub> 7  |

| Function            |

|---------------------|

| HV <sub>OUT</sub> 6 |

| HV <sub>OUT</sub> 5 |

| HV <sub>OUT</sub> 4 |

| HV <sub>out</sub> 3 |

| HV <sub>OUT</sub> 2 |

| HV <sub>out</sub> 1 |

| HV <sub>out</sub> 0 |

| V <sub>PP</sub>     |

| NC                  |

| NC                  |

| Cathode             |

| Anode               |

| NC                  |

| AGnd                |

| AV <sub>NN</sub>    |

| NC                  |

| AV <sub>DD</sub>    |

| AGnd                |

| DV <sub>NN</sub>    |

| DV <sub>DD</sub>    |

| NC                  |

|                     |

| Pin # | Function |

|-------|----------|

| 51    | NC       |

| 52    | NC       |

| 53    | NC       |

| 54    | NC       |

| 55    | NC       |

| 56    | NC       |

| 57    | NC       |

| 58    | NC       |

| 59    | NC       |

| 60    | NC       |

| 61    | NC       |

| 62    | NC       |

| 63    | NC       |

| 64    | NC       |

| 65    | NC       |

| 66    | NC       |

| 67    | NC       |

| 68    | NC       |

| 69    | NC       |

| 70    | NC       |

| 71    | NC       |

| 72    | NC       |

| 73    | NC       |

| 74    | NC       |

| 75    | NC       |

| Pin # | Function             |

|-------|----------------------|

| 76    | NC                   |

| 77    | NC                   |

| 78    | NC                   |

| 79    | NC                   |

| 80    | EN                   |

| 81    | A0                   |

| 82    | A1                   |

| 83    | A2                   |

| 84    | А3                   |

| 85    | A4                   |

| 86    | DGnd                 |

| 87    | DV <sub>DD</sub>     |

| 88    | DV <sub>NN</sub>     |

| 89    | AGnd                 |

| 90    | Vsig                 |

| 91    | AV <sub>DD</sub>     |

| 92    | Byp-AV <sub>NN</sub> |

| 93    | Byp-AV <sub>DD</sub> |

| 94    | AV <sub>NN</sub>     |

| 95    | NC                   |

| 96    | NC                   |

| 97    | R <sub>SINK</sub>    |

| 98    | R <sub>SOURCE</sub>  |

| 99    | Byp-V <sub>PP</sub>  |

| 100   | V <sub>PP</sub>      |

NC=No Connect.

# **Pad Configuration (Not Drawn to Scale)**

#### **Pad Coordinates**

Chip size: 17004µm x 5480µm Center of die is (0,0)

| Pad Name             | Χ (μm) | Υ (μm)  |

|----------------------|--------|---------|

| EN                   | 6248.5 | -2514.5 |

| A0                   | 6653.5 | -2514.5 |

| A1                   | 7058.5 | -2514.5 |

| A2                   | 7463.5 | -2514.5 |

| А3                   | 7868.5 | -2514.5 |

| A4                   | 8273.5 | -2514.5 |

| Dgnd                 | 8320   | -2150   |

| DV <sub>DD</sub>     | 8320   | -1785.5 |

| DV <sub>NN</sub>     | 8320   | -1485   |

| Agnd                 | 8300   | -1185.5 |

| Vsig                 | 8300   | -819.5  |

| AV <sub>DD</sub>     | 8300   | -519.5  |

| Byp_AV <sub>NN</sub> | 8300   | -219.5  |

| Byp_AV <sub>DD</sub> | 8300   | 295.5   |

| AV <sub>NN</sub>     | 8300   | 595.5   |

| R <sub>SINK</sub>    | 8340   | 2538    |

| R <sub>SOURCE</sub>  | 7860   | 2538    |

| Byp_AV <sub>PP</sub> | 7313   | 2538    |

| $V_{pp}$             | 7013   | 2538    |

| HV <sub>OUT</sub> 31 | 6512.0 | 2129.5  |

| HV <sub>OUT</sub> 30 | 6065.0 | 2129.5  |

| HV <sub>out</sub> 29 | 5618.0 | 2129.5  |

| HV <sub>out</sub> 28 | 5171.0 | 2129.5  |

| HV <sub>OUT</sub> 27 | 4724.0 | 2129.5  |

| HV <sub>out</sub> 26 | 4277.0 | 2129.5  |

| HV <sub>out</sub> 25 | 3830.0 | 2129.5  |

| HV <sub>out</sub> 24 | 3383.0 | 2129.5  |

| HV <sub>out</sub> 23 | 2936.0 | 2129.5  |

| HV <sub>out</sub> 22 | 2489.0 | 2129.5  |

| HV <sub>out</sub> 21 | 2042.0 | 2129.5  |

|                      |        |         |

| Pad Name             | Χ (μm)  | Y (µm)  |

|----------------------|---------|---------|

| HV <sub>out</sub> 20 | 1595.0  | 2129.5  |

| HV <sub>out</sub> 19 | 1148.0  | 2129.5  |

| HV <sub>out</sub> 18 | 701.0   | 2129.5  |

| HV <sub>out</sub> 17 | 254.0   | 2129.5  |

| НV <sub>о∪т</sub> 16 | -193.0  | 2129.5  |

| HV <sub>out</sub> 15 | -640.0  | 2129.5  |

| HV <sub>out</sub> 14 | -1087.0 | 2129.5  |

| HV <sub>out</sub> 13 | -1534.0 | 2129.5  |

| HV <sub>out</sub> 12 | -1981.0 | 2129.5  |

| HV <sub>out</sub> 11 | -2428.0 | 2129.5  |

| HV <sub>out</sub> 10 | -2875.0 | 2129.5  |

| HV <sub>out</sub> 9  | -3322.0 | 2129.5  |

| HV <sub>out</sub> 8  | -3769.0 | 2129.5  |

| HV <sub>out</sub> 7  | -4216.0 | 2129.5  |

| HV <sub>out</sub> 6  | -4663.0 | 2129.5  |

| HV <sub>out</sub> 5  | -5110.0 | 2129.5  |

| HV <sub>OUT</sub> 4  | -5557.0 | 2129.5  |

| HV <sub>out</sub> 3  | -6004.0 | 2129.5  |

| HV <sub>out</sub> 2  | -6451.0 | 2129.5  |

| HV <sub>out</sub> 1  | -6898.0 | 2129.5  |

| HV <sub>OUT</sub> 0  | -7345.5 | 2129.5  |

| V <sub>PP</sub>      | -7693.5 | 2536.5  |

| Cathode              | -8072.5 | 2488.5  |

| Anode                | -7803   | 2236.5  |

| Agnd                 | -7825.5 | 725.5   |

| AV <sub>NN</sub>     | -7921.5 | 425.5   |

| AV <sub>DD</sub>     | -7837   | -972.5  |

| Agnd                 | -7817   | -1390.5 |

| DV <sub>NN</sub>     | -7823   | -1779   |

| DV <sub>DD</sub>     | -7823   | -2080.5 |